隨著雙流區經濟的快速發展,企業對辦公環境的需求日益增長,辦公室員工位批發和家具零售服務成為市場熱點。本文將探討雙流區辦公家具市場的現狀、優勢及選購建議,幫助企業和個人高效配置辦公空間。

一、雙流區辦公家具市場概述

雙流區作為成都的重要經濟區域,擁有眾多辦公家具供應商,提供從員工位、辦公桌到會議椅的全方位批發和零售服務。這些家具不僅注重實用性,還融合了現代設計理念,滿足不同企業的個性化需求。市場覆蓋范圍廣泛,包括航空港、華陽等核心商圈,方便客戶就近選購。

二、辦公室員工位批發的優勢

辦公室員工位批發是許多企業的首選,主要優勢包括:

- 成本效益:批量采購可享受折扣優惠,降低企業初始投入。

- 統一風格:確保辦公空間整體協調,提升企業形象。

- 高效交付:供應商通常提供定制和快速安裝服務,縮短裝修周期。

三、家具零售的靈活性與多樣性

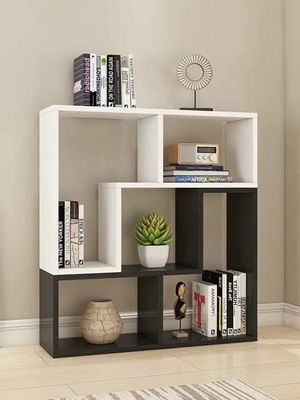

對于小型企業或個人用戶,家具零售提供了更多靈活性。客戶可以根據預算和空間大小,選擇單件或多件產品。雙流區的零售店提供多樣化的辦公家具,如 ergonomic 人體工學椅、多功能儲物柜等,注重健康與舒適性。

四、選購建議

在選擇辦公室員工位和家具時,建議關注以下幾點:

- 材質與耐用性:優先選擇環保材料,如E1級板材,確保長期使用安全。

- 功能設計:考慮儲物空間、線纜管理等細節,提升工作效率。

- 售后服務:選擇信譽良好的供應商,提供保修和維護支持。

五、結語

雙流區的辦公室員工位批發和家具零售服務為企業提供了便捷的解決方案。通過合理規劃,企業可打造高效、舒適的辦公環境,助力業務發展。建議在選購前實地考察或咨詢專業顧問,以獲得最佳性價比。